# Access to Advanced Packaging and Test

**Brett Hamilton**

## Heterogeneous Integration & 2.5D/3D Packaging

## Heterogeneous 3D

## Background

Must meet cost and schedule

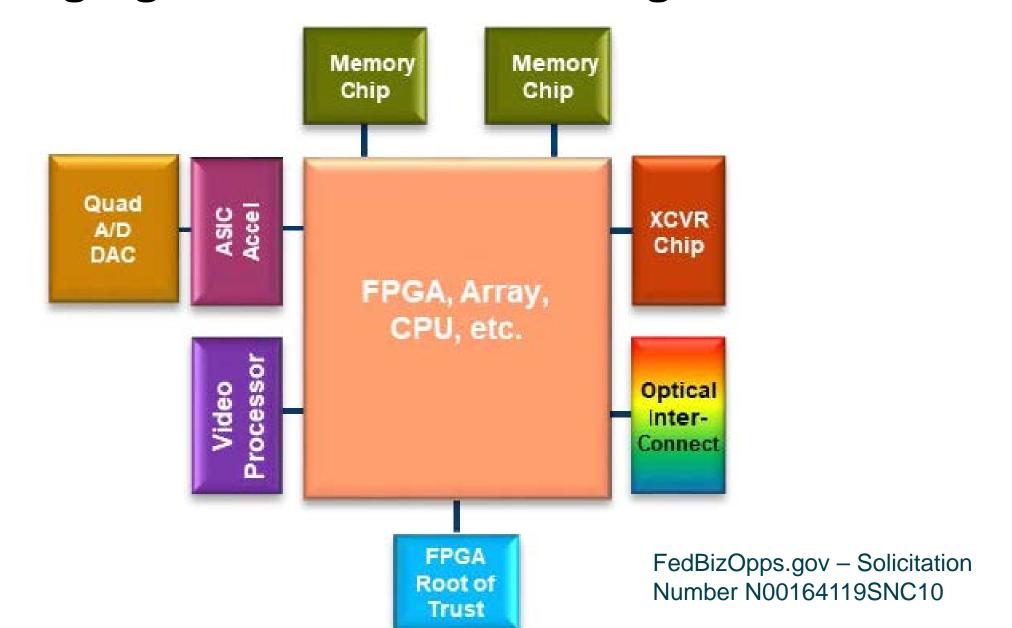

Source: Intel – Accelerating Innovation Through Chiplets OCP/ODSA Workshop, 6/10/2019

#### **World Leaders**

#### Industry Giants TSMC and Intel Vow to Focus on 3D IC Packaging (1)

Demand for high-performance computing (HPC) chips is exploding. These superspeedy chips are critical for data centers and cloud computing infrastructures to support new performance-hungry technologies such as artificial intelligence (AI) and 5G...... Heterogeneous integration offers a potential answer as an advanced packaging technology designed to meet these skyrocketing performance demands on HPC chips and open the door to a whole new world of 3D integrated circuits (ICs).

(1) https://blog.semi.org/technology-trends/industry-giants-tsmc-and-intel-vow-to-focus-on-3d-ic-packaging

So important are 3D ICs that Intel and TSMC representatives speaking at the recent Heterogeneous Integration Summit hosted by SEMI Taiwan in Taipei declared that the packaging technology will all but dictate the future of the industry.

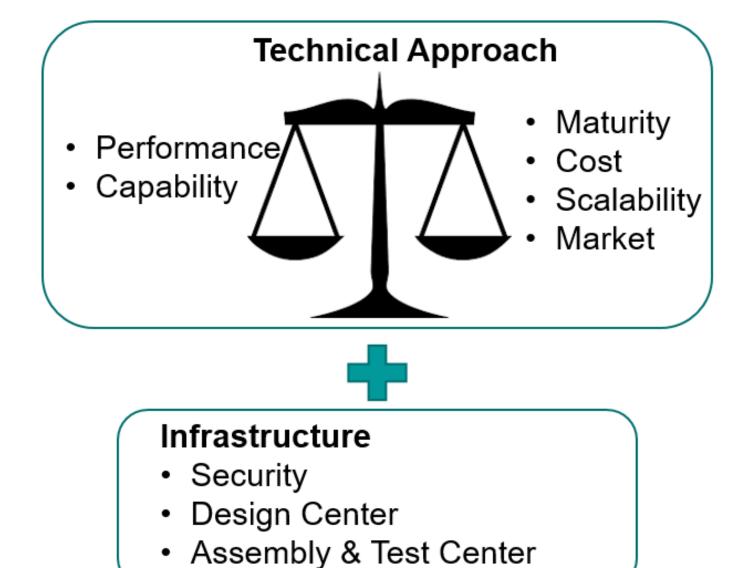

## Approach

Leveraging SOTA: While Allowing Customization!

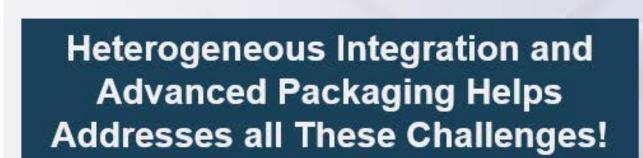

Custom configurations of chiplets allows DoD to optimize SWaP and performance to meet specific DoD weapon system specification. This modular approach is critical for rapid technology transition and for intellectual property (IP) re-use, reducing cost.

### SHIP Digital vs SHIP RF

#### Solution

## Results and Impact

#### **Technology is Commercially Available**

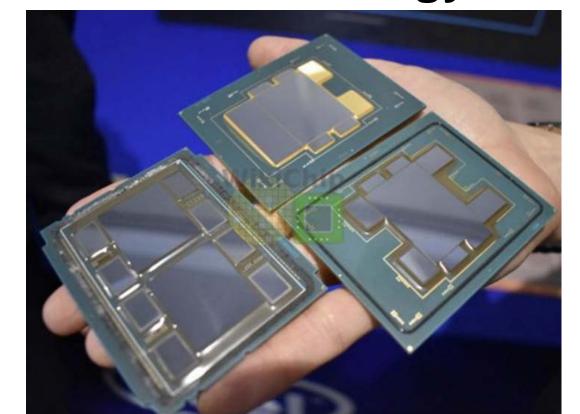

Intel revealed three new packaging technologies at SEMICON West: These new technologies enable massive designs by stitching together multiple dies into one processor. Building upon Intel's 2.5D EMIB and 3D Foveros tech, the technologies aim to bring near-monolithic power and performance to heterogeneous packages.

NEC's Latest Vector Processor - The chip utilizes **TSMC**'s second-generation chip on wafer on substrate (CoWoS) technology with NEC's implementation developed in collaboration with TSMC and Broadcom.

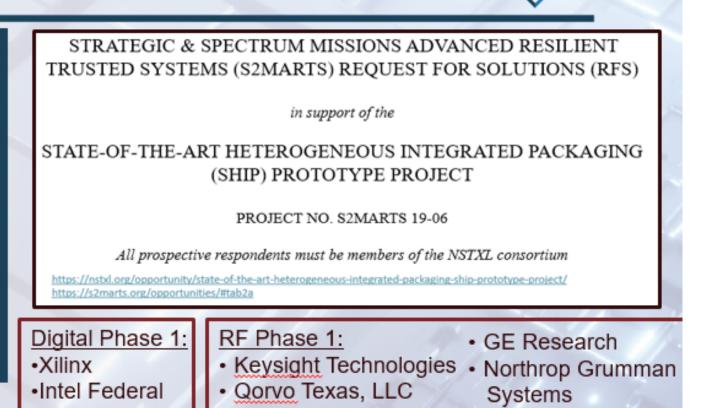

#### TRANSITION TO SHIP DIGITAL & RF

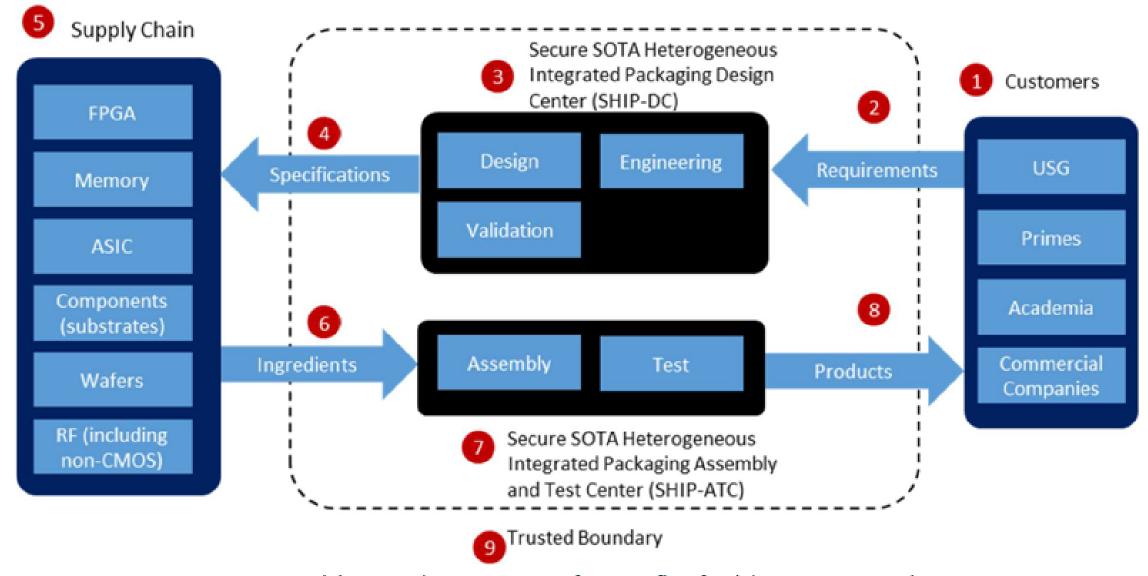

Develop domestic manufacturing capabilities for secure, SOTA, and reliable heterogeneous integrated packaging and test to meet the needs of the USG, including military and aerospace applications

- SHIP design center

- SHIP assembly and test center

Custom configurations that can include ASIC's and structured ASIC's allow the Primes to customize performance to meet their particular DoD weapon system specification. This is critical for rapid technology transition and sustainability.

### **SHIP Initiative**

Notional design and prototype manufacturing flow for delivering secure and SOTA packaging meeting the needs of defense and aerospace applications.